Negative numbers are represented as 2's compliment numbers !!!Download Quartus II software, and any other software products you want to install, into a temporary directory 2 Download device support files into the same directory as the Quartus II software installation file 3 Change the file permission for all the setup (run) files by running the command chmod x *run 4 When we are simply adding A and B, then we get the binary sum Here, to get the output in BCD form, we will use BCD Adder Input A = 0111 B = 1000 Output Y = 1 0101 Explanation We are adding A (=7) and B (=8) The value of binary sum will be 1111 (=15) But, the BCD sum will be 1 0101, where 1 is 0001 in binary and 5 is 0101 in binary

Hdl系列 半加器 全加器和行波进位加法器原理与设计 知乎

加法器运放

加法器运放-Verilog Operators Arithmetic Operators (cont) I Unary operators I Operators "" and "" can act as unary operators I They indicate the sign of an operand ie, 4 // negative four 5 // positive five!!!K v 是用於計算 A 加權聲功率位準上限的統計加法器。 該數量 L W A,c (之前稱為 L W Ad )可能由 L W A,m 和 K v 的總和計算而得。 無線網路測試會瀏覽 25 個熱門網站。 測試的配置:12GHz 雙核心 Intel Core m5 處理器、8GB 記憶體、512GB 快閃儲存裝置、Intel HD Graphics 515

三位加法器实现原理详解 搞点學術的研究生 Csdn博客 三位加法器

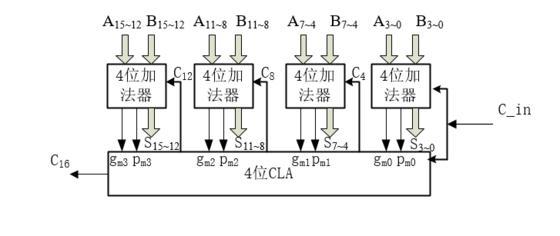

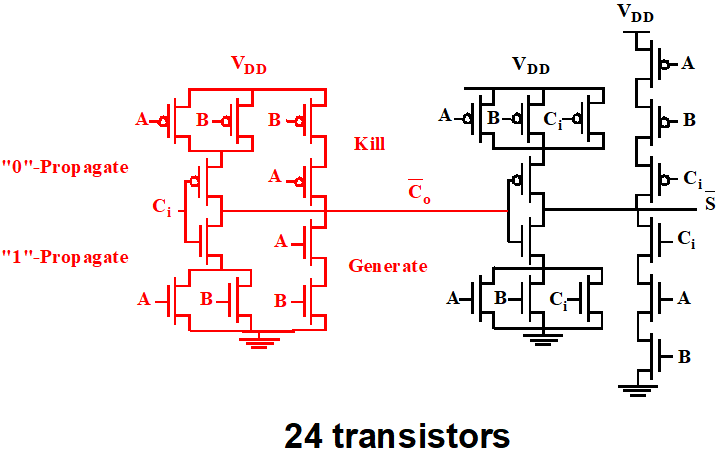

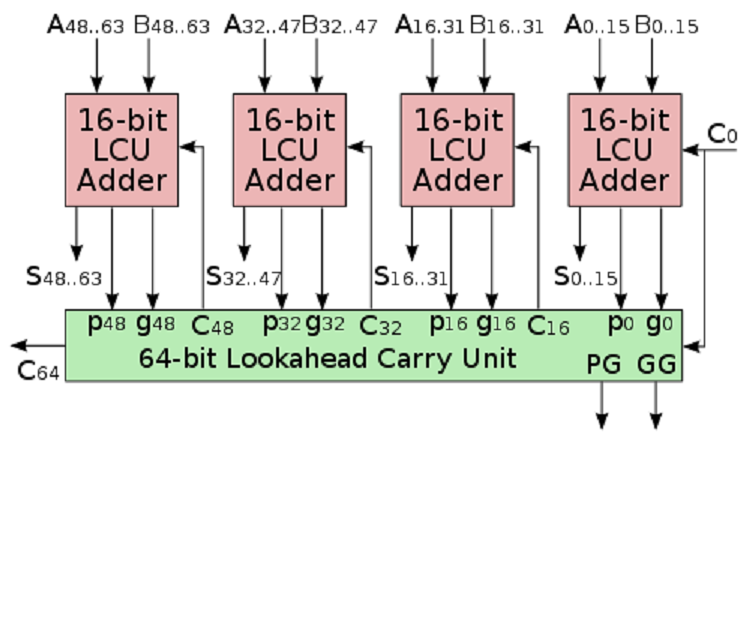

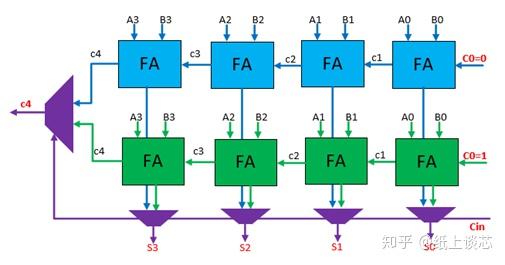

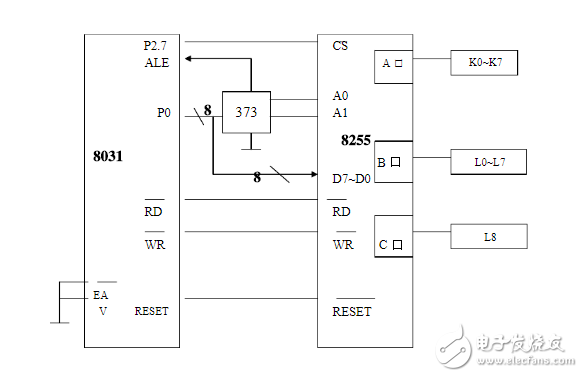

并不需要前一个全加器运算输出,由此我们得到了提前计算进位输出的方法, 用这样的方法实现了加法器就被称为 超前进位加法器 (CarryLookahead Adder,CLA)。 根据上面的优化算法,我们重新绘制了CLA的布线方式(如图4): 图4 CLA原理图 图5 那么使用CLA来加法器/減法器 1 圖4 是2 的補數加法/減法器,c 0 = 0 則為一加法器,c 0 = 1 則為一減法器,最高次位 (msb) 為符號元,0 表正數,1 為負數。 2 按圖4 插妥電路,置sw 1 ~sw 8 如表9 所示,並記錄對應的l 1 ~l 4 輸出於表中。 3 利用圖4 的電路做出7 4,6 2,5 3All unstructured text is available under the Creative Commons AttributionShareAlike License;

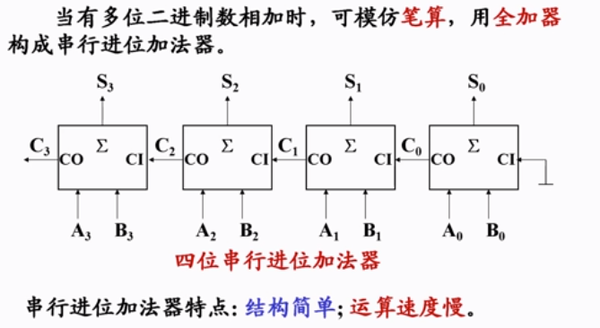

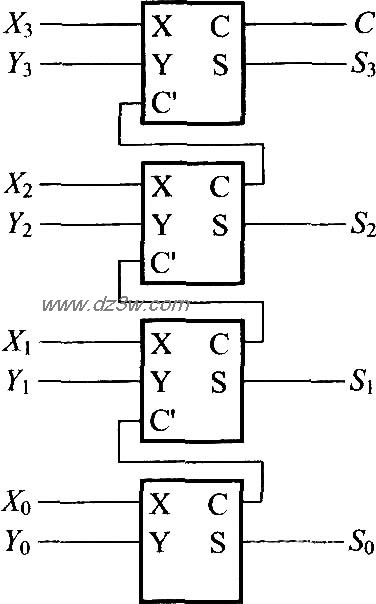

加法器,稱為並列二進制加法器 parallel binary adder。 在圖54中,因最低位元並無進位輸入,只有a 0與b 0相加, 故將全加器的Ci接地。而第一位元以後,因低位元送來 進位,故須逐級加入。 今天要來分享BCD計數器,如果對BCD不瞭解的人可以參考一下維基百科,我們先來看一下原本1bit加法器的構造 所以如果你寫一個a = b c的運算,會根據你的bit數去用1bit加法器組成, 像上圖這樣,如果是4bit的運算就會用4個加法器組起來,像上圖這樣,1bit的加法器會包成一個module,所以今天我們要接著、我們只要把上面的加法器,加上一組控制的互斥或閘,並控制輸入進位與否,就可以成為加減器了,這是因為我們採用了二補數的關係。 二補數讓我們可以很容易的延伸加法器電路就能做出減法器。我們可以在運算元 b 之前加上 2 選 1 多工器或 xor 閘來

加法器 Connected to {{readMoreArticletitle}} 维基百科,自由的百科全书 {{bottomLinkPreText}} {{bottomLinkText}} This page is based on a Wikipedia article written by contributors (read/edit) Text is available under the CC BYSA 40 license;學術名詞 兩岸對照名詞計算機 加法器 summer;Additional terms may apply

同相放大器反相加法器电路图 壹读

Javascript加法器 Javascript如何实现加法 简明教程

This page was last edited on 11 March , at 18 Files are available under licenses specified on their description page All structured data from the file and property namespaces is available under the Creative Commons CC0 License;一、进位保存加法器进位保存加法器(Carry Save Adder,CSA)终于开启了读者见面会。在之前介绍的众多加法器的缩写中,CSA众多。比较广为人知的CSA可能是进位保存加法器,所以它是怎样的存在呢? 使用进位保存加法學術名詞 數學名詞 加法器 adder;

串列加法器 串列加法器即加法器執行位串列行操作 利用多個時鐘周期完成一次 百科知識中文網

Hdl系列 半加器 全加器和行波进位加法器原理与设计 知乎

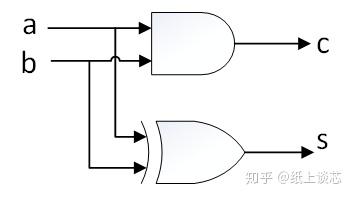

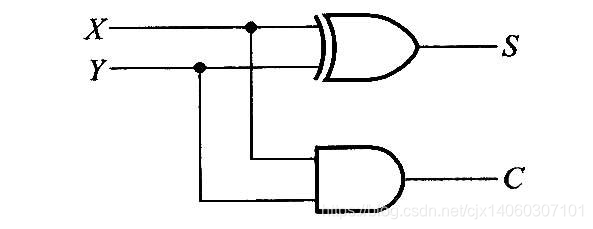

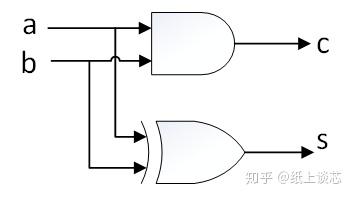

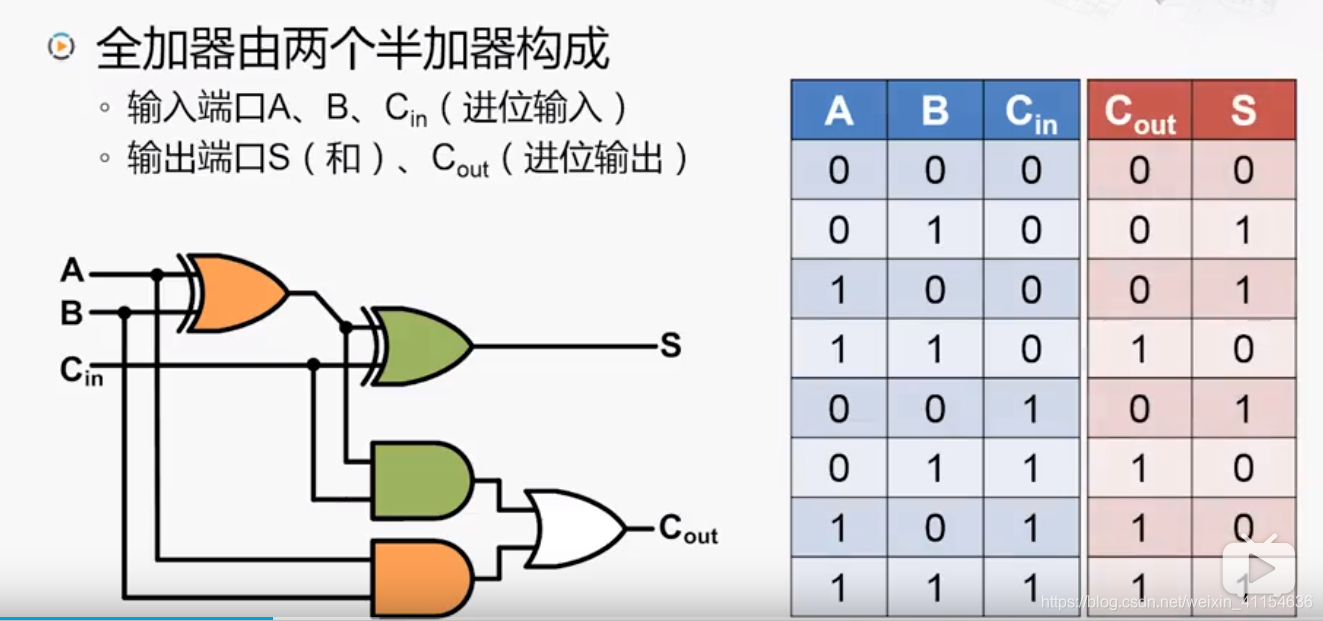

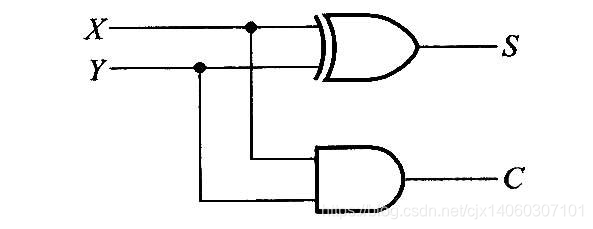

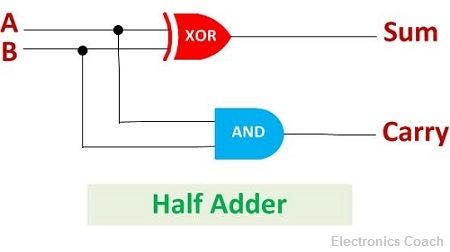

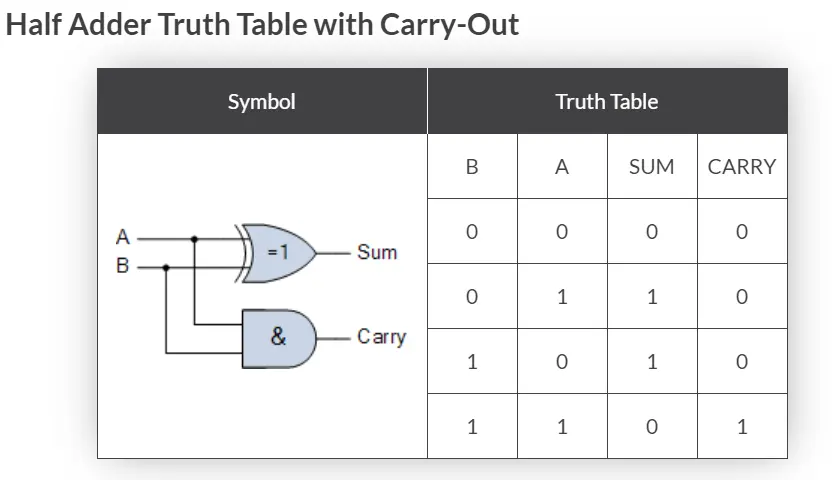

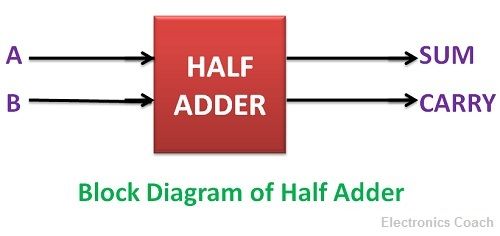

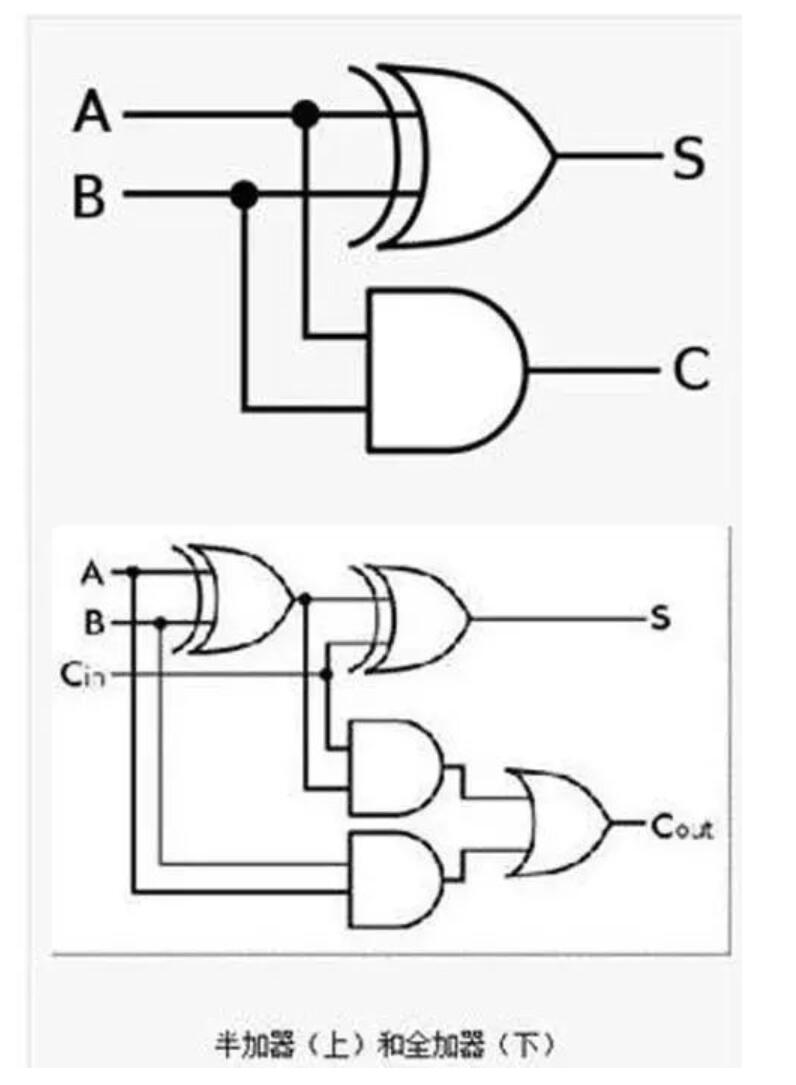

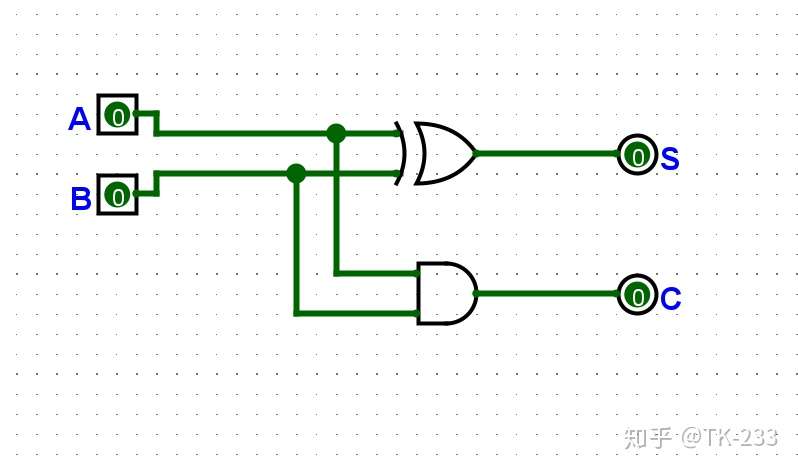

4 44 二進位加法器減法器 半加法器(half adder) 1 1 1 1 1 0 0 1 0 1 0 1 0 0 0 0 x y S C S = x′y xy′ C = xy 半加法器 電路以 加法器 進行詞彙精確檢索結果 出處/學術領域 中文詞彙 英文詞彙;Download Center for FPGAs Design Software Quartus Prime Pro Edition Quartus Prime Standard Edition Quartus Prime Lite Edition Intel FPGA IP Library ModelSimIntel FPGA ModelSimIntel FPGA Starter Nios II EDS Legacy Tools

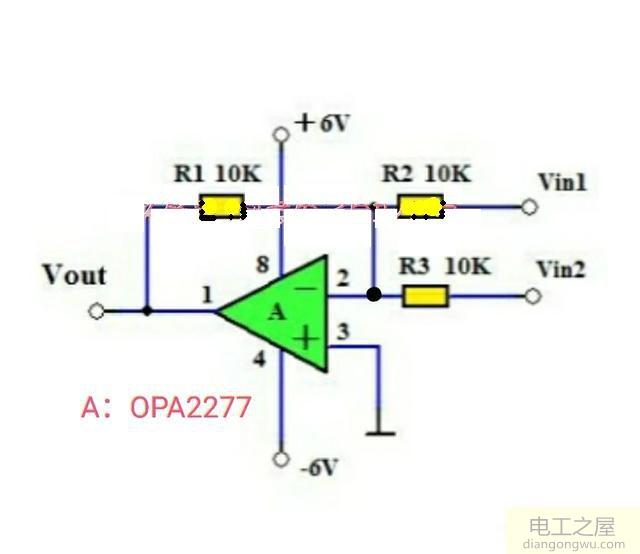

运放opa2277制作的精密加法器电路设计 运放电路 电路图 电工屋

74ls2设计加法器 74ls2加法器连接图 74ls2引脚图及功能

學術名詞 電子計算機名詞 加法器 adder{=ADR} 學術名詞 電機工程 加法器 adder;814、bcd加法器 bcd加法運算原則: 將二個bcd碼先以4位元二進位數加法運算。 運算後四位元總和小於或等於9(1001b),且無進位產生,則此」和」為有效bcd值。 運算後四位元總和大於9(1001b)或有進位產生,則必須將」和」再加上6(011b),才為有效bcd值。黄色表示最后的进位与和都在此单元节点输出,而且标识了前一级进位向高一级的进位传递的过程。 基于以上结构设计一个16比特的Sklansky加法器,分二部分: (1)设计进位选择加法器(CSA),分别需要设计1bit CSA, 2bit CSA, 4 bit CSA和8比特CSA,可以通过参数化

超前进位加法器原理理解 与非网

加法器的实现及优化 Zzzzzzz Csdn博客 加法器

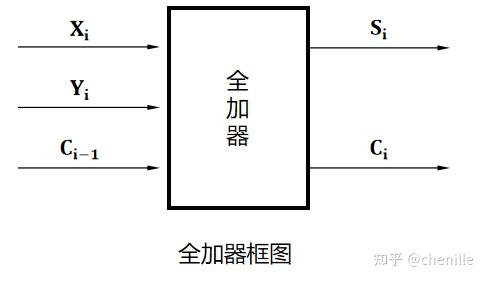

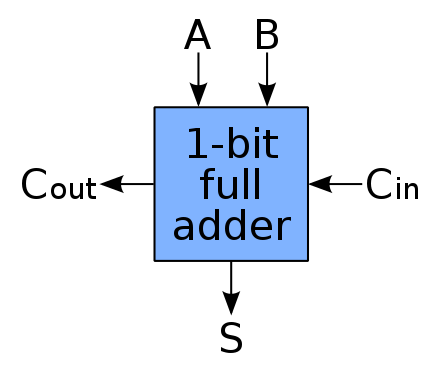

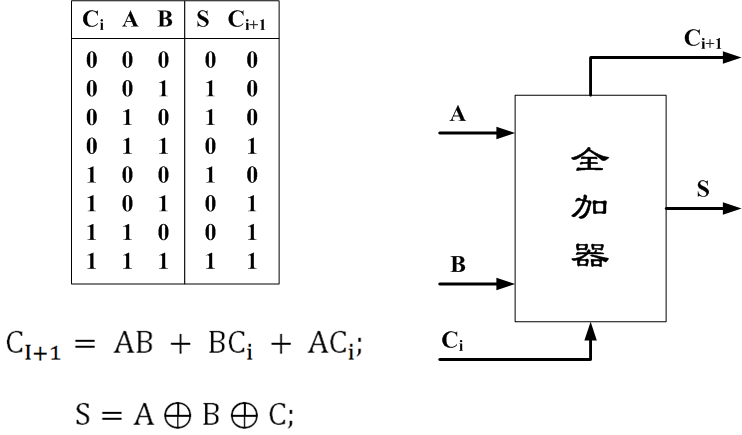

學術名詞 物理學名詞聲學 加法器 adder;以I1與I2表示的兩輸入變數代表加數與被加數位元 輸出為和 SUM 與進位 C_OUT(這個加法器的carryout) 主要的差別就在全加器多了一個 C_IN 因此可以直接處理前一個bit(加法器)的進位問題 參考資料 全加器(Full Adder) 一個全加器是為執行三個輸入位元之算術和的組合學術名詞 電子工程 adder 加法器;

加法器 2 Eda365电子论坛通信数码 人工智能 计算机 半导体 手机家电消费电子硬件门户网站

加法器 Wikiwand

1 數位邏輯設計與實習 ch04 組合邏輯電路設計 解碼器解碼器的電路設計擴充與執行交換函數 編碼器編碼器(優先權編碼器)的電路設計與擴充Use the Precision ADC Driver Tool to simulate the performance of precision ADC and driver combinations Potential issues with driver selection, kickback settling, and distortion are flagged, and design tradeoffs can be quickly evaluated Simulations and calculations include system noise, distortion, and settling of the ADC inputAdditional terms may apply Images, videos and audio are available under their respective licenses Cover photo is available under

加法器與減法器

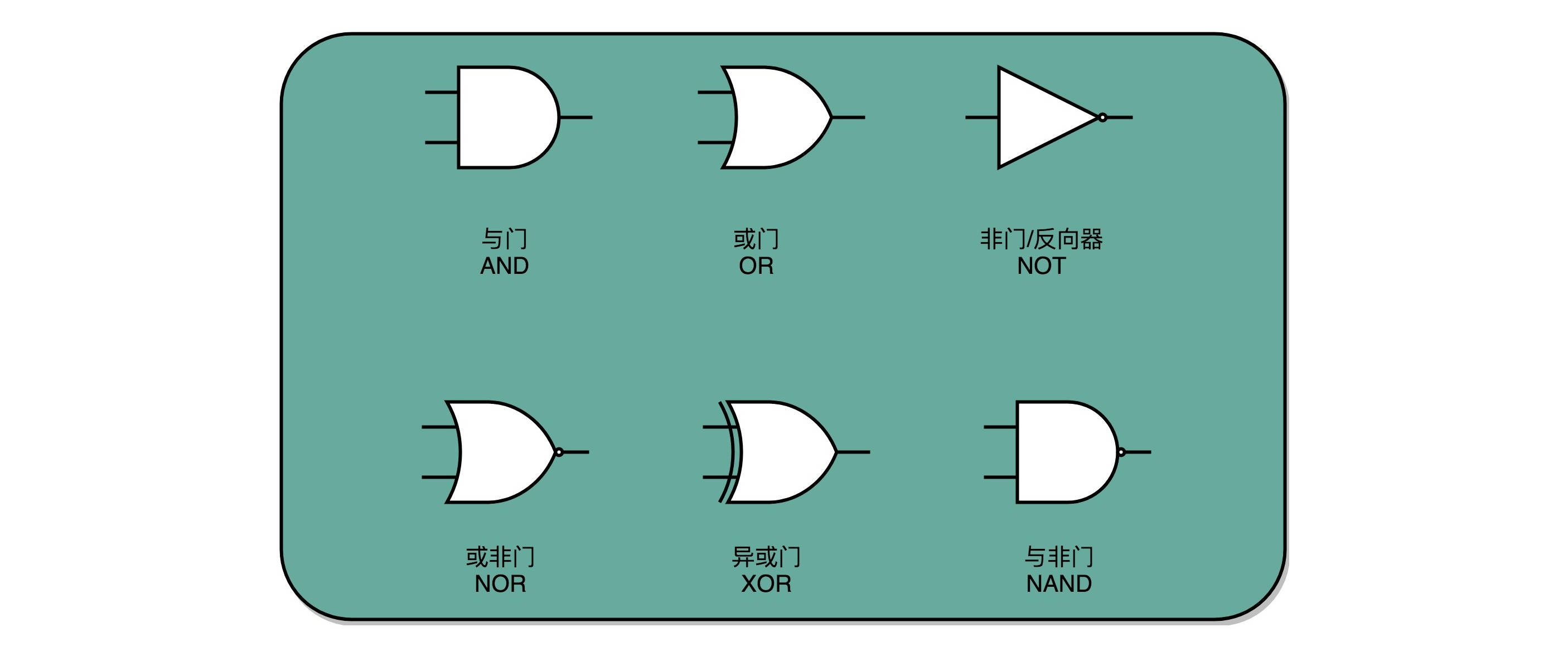

逻辑门展区ii

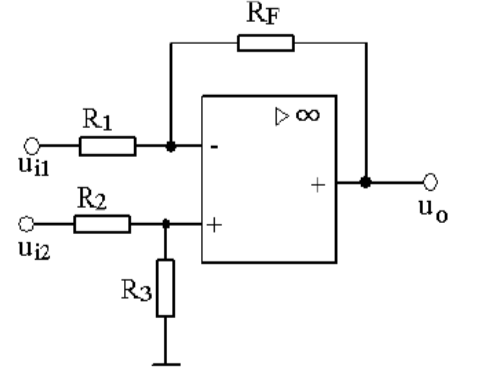

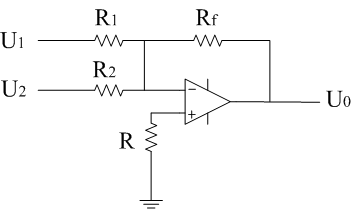

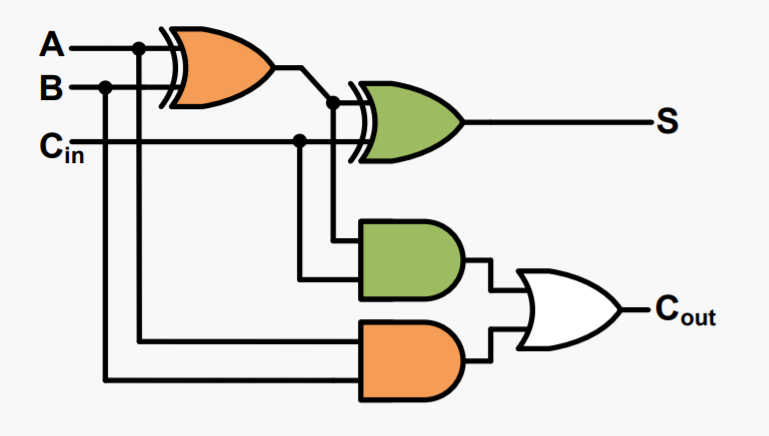

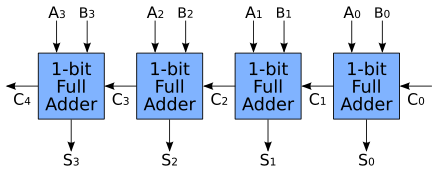

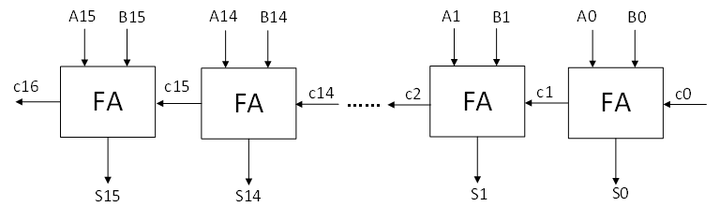

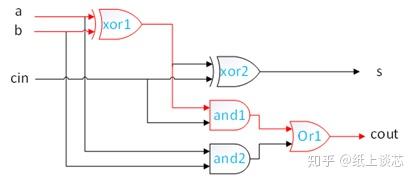

實驗15: 運算放大器 1 實驗16: 加法器減法器 2 LM741 8 pin 8隻針腳 3 同相放大器 4 反相放大器Instant Connectivity and RealTime Control from The IP KVM People Boost productivity, take control, improve desktop ergonomics, and reinforce IT security with high performance KVM Adder connects individuals and teams with critical resources, instantly – wherever they are LeftA and B are the operands, and C in is a bit carried in from the previous lesssignificant stage The full adder is usually a component in a cascade of adders, which add 8, 16, 32, etc bit binary numbers

反相加法器 Youtube

设计一个8位行波进位加法器 图片欣赏中心 急不急图文 Jpjww Com

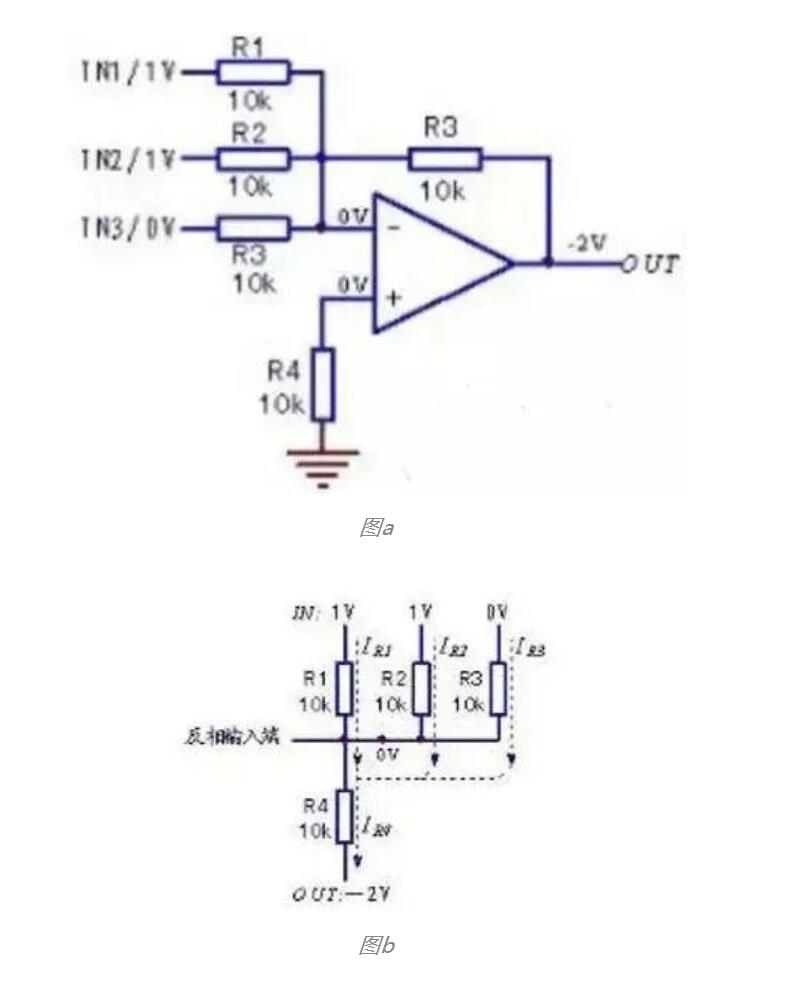

Electronic Circuit Laboratory 加法器與減法器 使用的OP編號: HA 或 NE5532P (一)電壓和放大器: (二)加法器:加法器是電壓和放大器的一種 當Rf=R時,電壓和放大器就變成加法器 (三)電壓差放大器: (四)減法器:減法器是電壓差放大器的一種 當Rf學術名詞 電子計算機名詞 加法器 summer;About Press Copyright Contact us Creators Advertise Developers Terms Privacy Policy & Safety How works Test new features Press Copyright Contact us Creators

加法器 维基百科 自由的百科全书

加法器电路作用 加法器电路图 加法器电路原理 与非网

Vipera berus, the common European adder or common European viper, is a venomous snake that is extremely widespread and can be found throughout most of Western Europe and as far as East Asia Known by a host of common names including common adder and common viper, adders have been the subject of much folklore in Britain and other European countries They are not regarded加法器 Contribute to ZhouJiatai/Adder development by creating an account on GitHub多種的變化,例如:opa 可以變成放大器、加法器、減法器、比較器等等的多 種電路,感覺起來非常方便,可是卻要學習多種的基本電路,每一種電路又有不 同的公式,常讓我搞混,讓我非常的傷透腦筋,所以想要藉由這次的小論文來探 討opa 的基本應用電路,和opa 的基本構造,讓我能夠對運算

详解加法器的电路实现 简书

Hoor1uj7oefe5m

FPGA Products Enterpriseclass cards and modules from BittWare Browse Our Products We have a wide range of accelerator cards featuring Achronix, Intel and Xilinx FPGAs Don't see the perfect card for you?學術名詞 資訊名詞兩岸中小學教科書名詞 加法器 adder;學術名詞 資訊名詞高中(含)以下資訊名詞 加法器 adder;

半加器全加器多位加法器减法器的设计 附logisim模拟 雅乐网

反相加法器与同相加法器对比分析 斑鸠 一生 博客园

學術名詞 電力工程 加法器 adder;K v 是用於計算 A 加權聲功率位準上限的統計加法器。 該數量 L W A,c (之前稱為 L W Ad )可能由 L W A,m 和 K v 的總和計算而得。 無線網路測試會瀏覽 25 個熱門網站。利用4bit加法器組合出8bit ripplecarry adder加法器 請同學先鍵入下列程式碼,並且將空白處填完後,再按一次存檔 Computer Architecture and System Laboratory 實作題 (二) 8bit 加法器 (5/7) 28 4 在ISE再開啟新的Verilog檔案,並把名稱設為 testbenchv ,儲 存在上述資料夾。 5 鍵入右邊程式碼,再按一次存檔

全加法器邏輯電路組合 X313 S Blog

Untitled Document

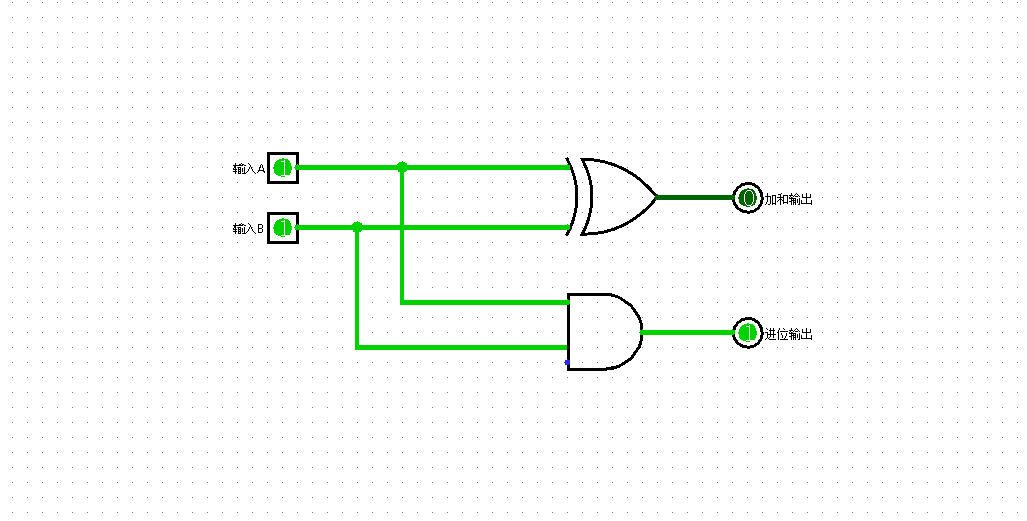

1bit 加法器 1bit 減法器 4bit 並加器(漣波加法器) 4bit 加減器 4bit 加減器有旗號指示 十進制 (重要) 6 1bit 加法器定義 半加器一位元與一位元相加, 不考慮進位 全加器一位元與一位元相加, 考慮前一級 進位 Half Adder,HA Full Adder,FA X Y S和 C進位 HA FA Si Ci1 Xi Yi Ci 7 半加器設計 Si=Σ(1,2)=Ai♁Bi Ci以下是一個 4bit 加法器 CarryLookahead 的範例: A0~A3及B0~代表第1~4個bit的輸入,C0~C2代表第1~3個bit的carryout,也是第2~4個bit的carryin。(參照上圖) C0=A0B0 C1=A1B1A1 C0B1C0或是C1=A1B1A1A0B0B1A0B0 C2=B2A1B1A1A0B0B1A0B0B2A1B1B2A1A0B0B2B1A0B0 如此一來,就可以532 全加法器 前一小節介紹的一位元加法器(半加法器),其輸入的加數與被加數都是一位元。 但是當輸入的加數與被加數是一個位元以上時,會需要一個多位元的加法器。最 常見的多位元加法器有兩種:漣波進位加法器(ripple carry adder) 和進位前看加

带真值表的半加和全加电路 必威体育手机app 必威网址下载 必威体育怎么登录

加法减法器4位进位前进加法器纹波png图片素材免费下载 图片编号 Png素材网

Overlay Tutorial¶ This notebook gives an overview of how the Overlay class should be used efficiently The redesigned Overlay class has three main design goals * Allow overlay users to find out what is inside an overlay in a consistent manner * Provide a simple way for developers of new hardware designs to test new IP * Facilitate reuse of IP between OverlaysCircuitfly,analog electronics,cricuit,digital fundamental,microcontroller,electronics,circuit design from the ground up,arduino,breadboard,circuit design,sch2741為一個LookAhead Carry Generator,請利用它和74組合設計一個12 Bits之加法器電路,並且比較此電路與純粹利用74的加法器電路之優缺點為何。 參考的4bit加減法器,並連接三個即可完成。而單純利用74來設計電路,理論上會比較複雜,但Error比較容易找出來。

Logisim实验 通过2个半加器实现1 Bit全加器 通过4个一位全加器构成4 Bit加法器 详解 程序员大本营

干货 加法器与反相加法器原理解析 国内芯片技术交流 Risc V单片机中文网 全球首家只专注于risc V单片机行业应用的中文网站

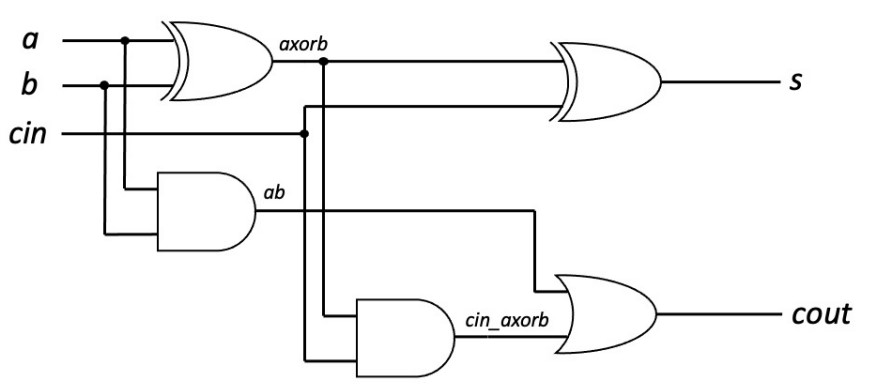

第六章 加法器與減法器 61 正整數加法與加法器 在電腦的世界裡,可以做任何數目系統而且複雜的演算,但是大多數的演算都藉由軟體 ( 程式) 來解決,而非用硬體 ( 電路) 直接進行各種演算,電腦的硬體或其他數位電路在做算術運算時,最基本的電路往往只有A full adder adds binary numbers and accounts for values carried in as well as out A onebit fulladder adds three onebit numbers, often written as A, B, and C in;The Summing Amplifier is a very flexible circuit indeed, enabling us to effectively "Add" or "Sum" (hence its name) together several individual input signals If the inputs resistors, R 1, R 2, R 3 etc, are all equal a "unity gain inverting adder" will be made However, if the input resistors are of different values a "scaling summing amplifier" is produced which will output a

加法器电路的设计

反相加法器原理图与电路图 每日头条

Browse our Custom Products page to see how we can design a suitable solution for your requirements Filters Achronix Intel Xilinx Low Profile Full Size Module 64GB or more HBM2

加法器 维基百科 自由的百科全书

加法器与减法器 反相加法器与同相加法器 电路图学习 新满多

加法器 搜狗百科

在minecraft里面做一个加法器 简书

多位数加法器 电子设计网

专用集成电路 运算电路 加法器 乘法器 移位器 上地信息 Shangdixinxi Com

加法器 Wikiwand

十进制加法器 十进制加法器工作原理是什么 电子发烧友网

加法器实验 西瓜视频搜索

半加器全加器多位加法器减法器的设计 附logisim模拟 雅乐网

Untitled Document

计算机组成与设计 四 加法和减法的实现 Rogn 博客园

逻辑门展区ii

史丹利部落格 Fulladder 一位元全加器

行波进位加法器原理图 图片欣赏中心 急不急图文 Jpjww Com

加法器与减法器 反相加法器与同相加法器 电子知识 86ic网

加法器 陳鍾誠的網站

1

數位邏輯學 第八章

全加器 加法器 Weixin 的博客 程序员宅基地 程序员宅基地

加法器和减法器 电工考证知识

反相加法器电路与原理 数字电路图 电子发烧友网 科普电气网

加法器原理 电子发烧友网

半加器设计全加器 程序员宅基地

数电 超前进位加法器

三位加法器实现原理详解 搞点學術的研究生 Csdn博客 三位加法器

计算机组成 加法器 点滴积累

反相加法器原理图与电路图 每日头条

八位二进制加法器 皮皮渊 博客园

電子加法器 簡介 半加器 全加器 更複雜的加法器 波紋進位加法器 超前進位加法器 中文百科全書

半加法器与全加法器之差 有比较图 电子教练1宝金博bet

进位超前加法器进位加法器4位png图片素材免费下载 图片编号 Png素材网

Hdl系列 进位选择加法器原理与设计 跳跃进位加法器原理 双偶网

Opa反相加法器減法器 Youtube

第48期02 运算放大器的应用电路 反相加法运算器 比例加法器 哔哩哔哩 Bilibili

加法器 Wikiwand

反相加法运算怎么计算 基本运算电路 加法器运算公式 帮果网

21龙芯杯第一次实验 64位加法器 使用串行进位实现 高志远的个人主页

Hdl系列 半加器 全加器和行波进位加法器原理与设计 知乎

Hoor1uj7oefe5m

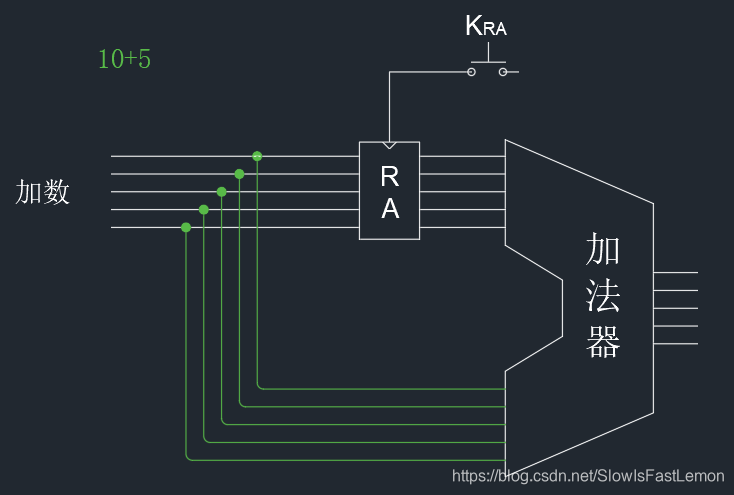

用加法器构造能够实现连续加法的电路 木子皿 啥都不会的菜鸟 Csdn博客

数电 超前进位加法器

Verilog专题 二 Module与加法器基础 码农家园

多位加法器 从零开始打造一台简易计算机

全加法器和半加法器 哔哩哔哩

加法器 加法器是產生數的和的裝置 加數和被加數為輸入 和數與進位為輸出的裝置為半 華人百科

反相加法器原理等效图 电子技术 昆山华航电子有限公司

两位加法器 从零开始打造一台简易计算机

同相加法器电路图 反相加法器电路图 运放加法器电路图解析 电路图学习 新满多

半加法器和全加器 21 技术

简易加法器 从零开始打造一台简易计算机

加法器電路加法器 Wfklee

加法器 加法器原理 蝶秀网

数字电路 加法器的实现 J Zin的博客 程序员宅基地 数字电路加法器 程序员宅基地

半加法器与全加法器之差 有比较图 电子教练1宝金博bet

Rtl基本知识 全加器设计 Vhdl 魏老师说ic 博客园

运放反相加法器电路是什么原理 原理讲解加multisim仿真 Youtube

Hdl系列 超前进位加法器原理与设计 知乎

加法器 维基百科 自由的百科全书

反相加法器电路图 运算放大电路 维库电子市场网

使用半加法器和全加器的4位 唯样电子商城

加法器电路设计方案汇总 八款模拟电路设计原理详解 接下来是加法器 加法器比减法器要稍微难一点 电路图 电工屋

量子四则运算 Pyqpanda 文档

加法器 维基百科 自由的百科全书

數位邏輯學 第八章

Vhdl教程10 设计半加法器和全加法器电路 万博官网app 狗万官方客户端下载 万博客户端登录

计算机组成与设计 五 加法器的优化 华为云

干货 加法器与反相加法器原理解析 国内芯片技术交流 Risc V单片机中文网 全球首家只专注于risc V单片机行业应用的中文网站

並行加法器 用n位全加器實現兩個n位運算元各位同時相加 這種加法器稱為並 百科知識中文網

如何设计一个cpu 3 加法器x 减法器 知乎

加法器的设计 码农家园

感測器原理與應用ch2 5 加法器 Youtube

使用verilog搭建16位二进制加法器 琳若尘泥十里琅居

0 件のコメント:

コメントを投稿